Processeurs EPYC: AMD termine avec succès Venise de Venise dans TSMC N2 à partir de 34 commentaires

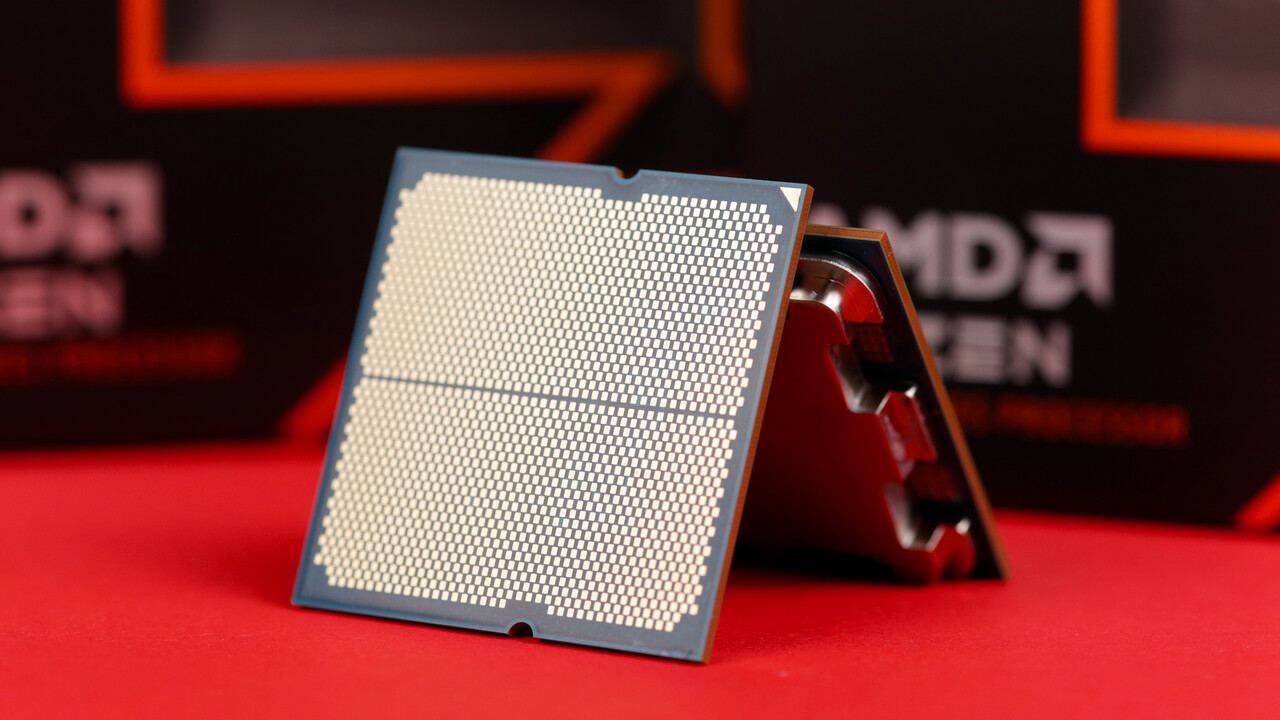

Image: AMD

AMD a réussi la prochaine génération de la prochaine génération de processeurs EPYC pour le segment HPC qui s'exécute sous le nom de code Venise, dans le nouveau processus de fabrication N2 TSMC avec des nanofeuilles. De plus, AMD a réussi dans les premiers tests et validations de l'EPYC de 5e génération dans le TSMC Arizona Fab 21.

Produit industriel du premier HPC dans TSMC N2

La prochaine génération de processeurs EPYC alias Venise est le monde industriel du premier produit HPC qui a terminé une bande réussie dans le processus de fabrication TSMC N2 avec des nanofeuilles. Le PDG d'AMD, le Dr Lisa SU et le PDG de TSMC, le Dr CC Wei, a célébré cela démontreux avec une plaquette fabriquée en conséquence avec Venise CCD.

C'est dans la nouvelle production

TSMC avait annoncé le processus de fabrication N2 à l'été 2022 avec un début de production prévu en 2025 et, en passant à la porte tout autour (GAA), ou comme TSMC l'appelle: des nanofeuilles, 10 à 15% de plus avec la même consommation d'énergie ou une consommation d'énergie de 25 à 30% avec les mêmes performances. Une variante haute performance qui est maintenant utilisée dans le segment HPC pour AMD, ainsi qu'une version mobile sont prévues pour TSMC N2.

Les nanofeuilles ont brièvement expliqué

Les nanofeuilles ou les nanawires sont des structures bidimensionnelles avec une épaisseur inférieure à 100 nm. Ils sont sur les cartes routières de l'industrie des puces depuis des années et visent à rendre la technologie successeur de FINFET possible, qui utilise des transistors dans la structure des ailerons en trois dimensions. Les nanofeuilles sont utilisées pour la première fois avec une porte tout autour, car ce type de production dépend des «fils» minces.

Plus de détails sur la bite de la technologie de fabrication: Innovations hier, aujourd'hui et demain

AMD Venise devrait commencer l'année prochaine

Selon l'annonce actuelle d'AMD, la prochaine génération d'EPYC devrait démarrer le marché l'année prochaine. Venise Alias EPYC 9006 devrait à nouveau offrir un maximum de 8 places de puces avec jusqu'à 32 cœurs zen-6 et donc jusqu'à 256 cœurs provenant de la production de 2 nm.

En tant que « Turin Classic », l'alias EPYC 9005 actuel propose actuellement un maximum de 128 cœurs ZEN-5 avec 16 8 8 CCD de base et un maximum de 192 cœurs zen-5c avec 12 CCD de 16 kern comme « Turin dense ». Venise réduirait à nouveau le nombre de CCDS quatre fois plus large. Du côté officiel, AMD n'a pas encore annoncé de détails techniques sur Venise.

Tests réussis dans TSMC Arizona Fab 21

Bien que la production de N2 soit réalisée à Taïwan, les processeurs EPYC actuels de 5e génération doivent également être fabriqués aux États-Unis dans TSMC Arizona Fab 21. Là, AMD a réussi à terminer la « réduction », à savoir les tests initiaux après la production d'une nouvelle puce et la validation des processeurs.

Sujets: AMD EPYC Half -Conductor Industry Processor Server TSMC Source: AMD

Marc décrypte les processeurs en testant leurs performances pour le gaming, la création de contenu et l’intelligence artificielle.