Procesadores EPYC: AMD completa con éxito la Venecia de Venecia en TSMC N2 (34 comentarios)

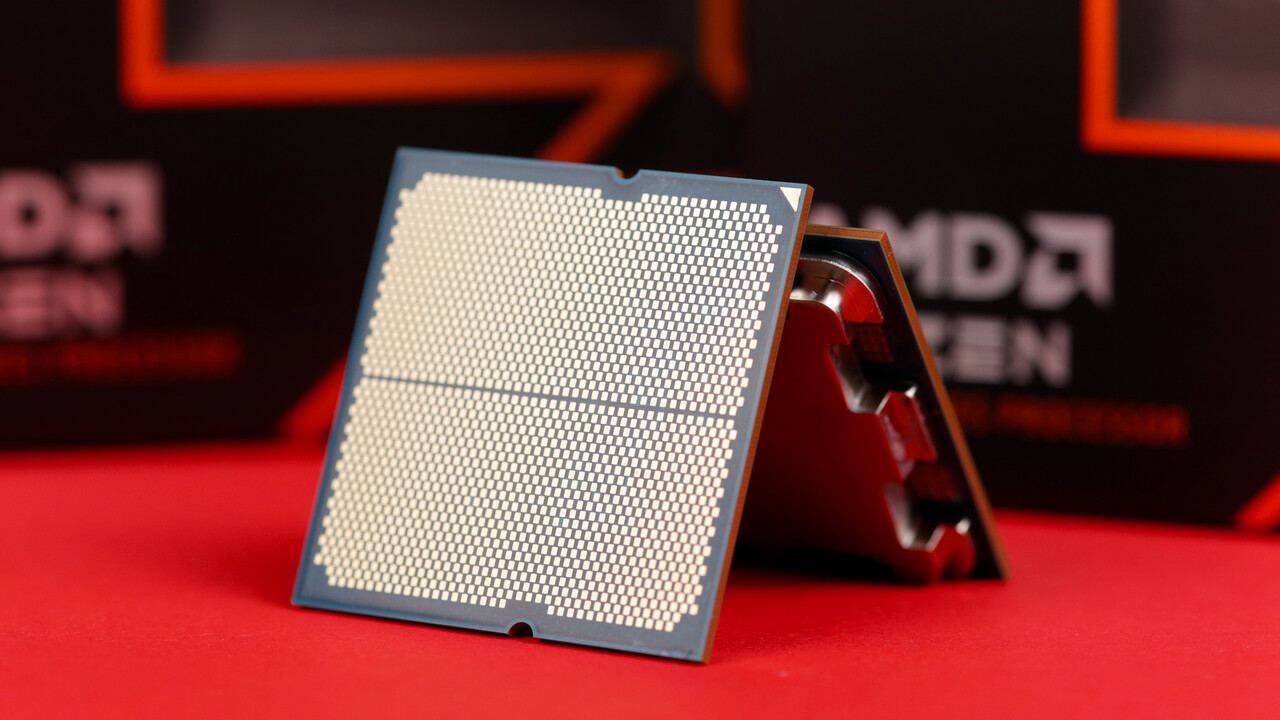

Imagen: AMD

AMD ha fabricado con éxito la próxima generación de procesadores EPYC para el segmento HPC, con nombre en código Venice, en el nuevo proceso de fabricación de nanohojas N2 de TSMC. Además, AMD ha completado con éxito las primeras pruebas y la validación del EPYC de quinta generación en TSMC Arizona Fab 21.

Producto industrial del primer HPC en TSMC N2

La próxima generación de procesadores EPYC, también conocidos como Venice, es el primer producto HPC del mundo industrial que completa con éxito una tira en el proceso de fabricación N2 de TSMC con nanohojas. La directora ejecutiva de AMD, Dra. Lisa Su, y el director ejecutivo de TSMC, Dr. CC Wei, celebraron esta demostración con una oblea fabricada correspondientemente con Venice CCD.

Está en la nueva producción.

TSMC había anunciado el proceso de fabricación N2 en el verano de 2022 con un inicio de producción previsto para 2025 y, al pasar al gate all around (GAA), o como lo llama TSMC: nanohojas, entre un 10 y un 15 % más con el mismo consumo de energía o entre un 25 y un 30 % más de consumo de energía con el mismo rendimiento. También está prevista una variante de alto rendimiento que ya se utiliza en el segmento HPC para AMD, así como una versión móvil para TSMC N2.

Nanohojas explicadas brevemente

Las nanohojas o nanocables son estructuras bidimensionales con un espesor inferior a 100 nm. Han estado en la hoja de ruta de la industria de los chips durante años y su objetivo es hacer posible la tecnología sucesora de FINFET, que utiliza transistores en una estructura de aletas tridimensional. Por primera vez se utilizan nanohojas con una puerta circundante, ya que este tipo de producción se basa en “alambres” delgados.

Más detalles sobre la tecnología de fabricación de dick: Innovaciones de ayer, hoy y mañana

Se espera que AMD Venice comience el próximo año

Según el anuncio actual de AMD, se espera que la próxima generación de EPYC llegue al mercado el próximo año. Venice Alias EPYC 9006 debería volver a ofrecer un máximo de 8 ranuras de chip con hasta 32 núcleos Zen-6 y, por lo tanto, hasta 256 núcleos de producción de 2 nm.

Como “Turin Classic”, el actual alias EPYC 9005 ofrece actualmente un máximo de 128 núcleos ZEN-5 con 16 CCD de 8 núcleos y un máximo de 192 núcleos zen-5c con 12 CCD de 16 núcleos como “Turin Dense”. Venecia volvería a reducir cuatro veces el número de CCDS. En el lado oficial, AMD aún no ha anunciado ningún detalle técnico sobre Venice.

Pruebas exitosas en TSMC Arizona Fab 21

Aunque la producción de N2 se realiza en Taiwán, los procesadores EPYC de quinta generación también se fabricarán en EE. UU., en la planta TSMC Arizona Fab 21. Allí, AMD completó con éxito la fase de “reducción”, es decir, las pruebas iniciales tras la producción de un nuevo chip y la validación de los procesadores.

Temas: AMD EPYC Semiconductor Industria Procesador Servidor TSMC Fuente: AMD

Marc analiza procesadores probando su rendimiento para gaming, creación de contenido e inteligencia artificial.