EPYC-processorer: AMD fuldender med succes Venedig i Venedig i TSMC N2 fra 34 kommentarer

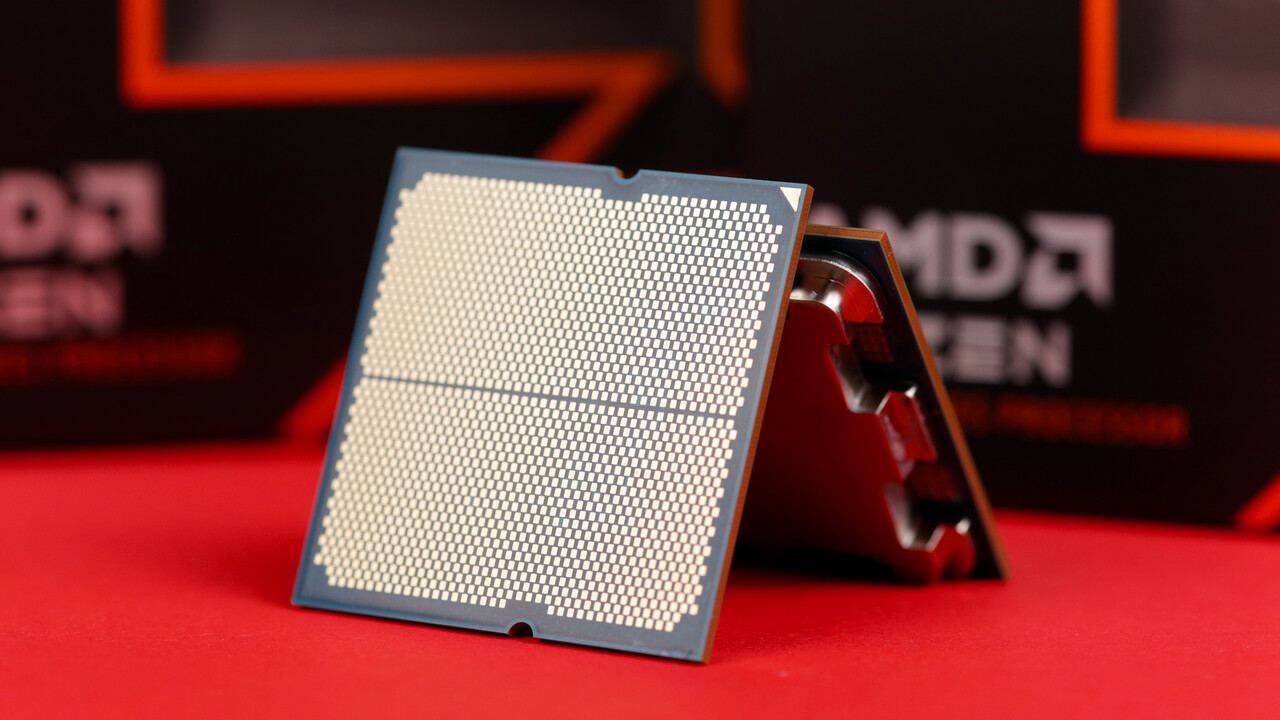

Billede: AMD

AMD har med succes fremstillet den næste generation af EPYC-processorer til HPC-segmentet, kodenavnet Venedig, i TSMC’s nye N2 nanosheet-fremstillingsproces. Derudover har AMD med succes gennemført tidlig test og validering af 5. generations EPYC på TSMC Arizona Fab 21.

Industrielt produkt fra den første HPC i TSMC N2

Den næste generation af EPYC-processorer alias Venedig er den industrielle verdens første HPC-produkt, der med succes fuldfører en strimmel i TSMC N2-fremstillingsprocessen med nanoark. AMD CEO Dr. Lisa Su og TSMC CEO Dr. CC Wei fejrede denne demonstration med en wafer fremstillet i overensstemmelse hermed med Venedig CCD.

Det er i den nye produktion

TSMC havde annonceret N2-fremstillingsprocessen i sommeren 2022 med en forventet produktionsstart i 2025 og, ved at flytte til gate all around (GAA), eller som TSMC kalder det: nanosheets, 10-15% mere med samme strømforbrug eller 25-30% mere strømforbrug med samme ydeevne. En højtydende variant, der nu bruges i HPC-segmentet til AMD, samt en mobilversion er planlagt til TSMC N2.

Nanosheets kort forklaret

Nanoplader eller nanotråde er todimensionelle strukturer med en tykkelse på mindre end 100 nm. De har været på chipindustriens køreplan i årevis og har til formål at gøre FINFETs efterfølgerteknologi, som bruger transistorer i en tredimensionel finnestruktur, mulig. Nanosheets bliver brugt for første gang med en omgivende port, da denne type produktion er afhængig af tynde “tråde”.

Flere detaljer om fremstillingsteknologi-pikken: Innovationer i går, i dag og i morgen

AMD Venice forventes at starte næste år

Ifølge AMD’s aktuelle meddelelse forventes den næste generation af EPYC at komme på markedet næste år. Venice AliasEPYC 9006 skulle igen tilbyde maksimalt 8 chip slots med op til 32 Zen-6 kerner og dermed op til 256 kerner fra 2nm produktion.

Som “Turin Classic” tilbyder det nuværende EPYC 9005-alias i øjeblikket maksimalt 128 ZEN-5-kerner med 16 8 8-kerne CCD’er og maksimalt 192 zen-5c-kerner med 12 16-kerne CCD’er som “Turin Dense”. Venedig ville igen reducere antallet af CCDS med fire gange. På den officielle side har AMD endnu ikke annonceret nogen tekniske detaljer om Venedig.

Vellykket test på TSMC Arizona Fab 21

Selvom N2-produktion udføres i Taiwan, skal den nuværende 5. generation af EPYC-processorer også fremstilles i USA på TSMC Arizona Fab 21. Der har AMD med succes gennemført “krympningen”, det vil sige den indledende test efter produktionen af en ny chip og valideringen af processorerne.

Emner: AMD EPYC Half-Conductor Industry Processor Server TSMC Kilde: AMD

Marc afdækker processorer ved at teste deres ydeevne til gaming, indholdsproduktion og kunstig intelligens.