EPYC Processors: AMD Successfully Completes Venice Processing in TSMC N2 from 34 comments

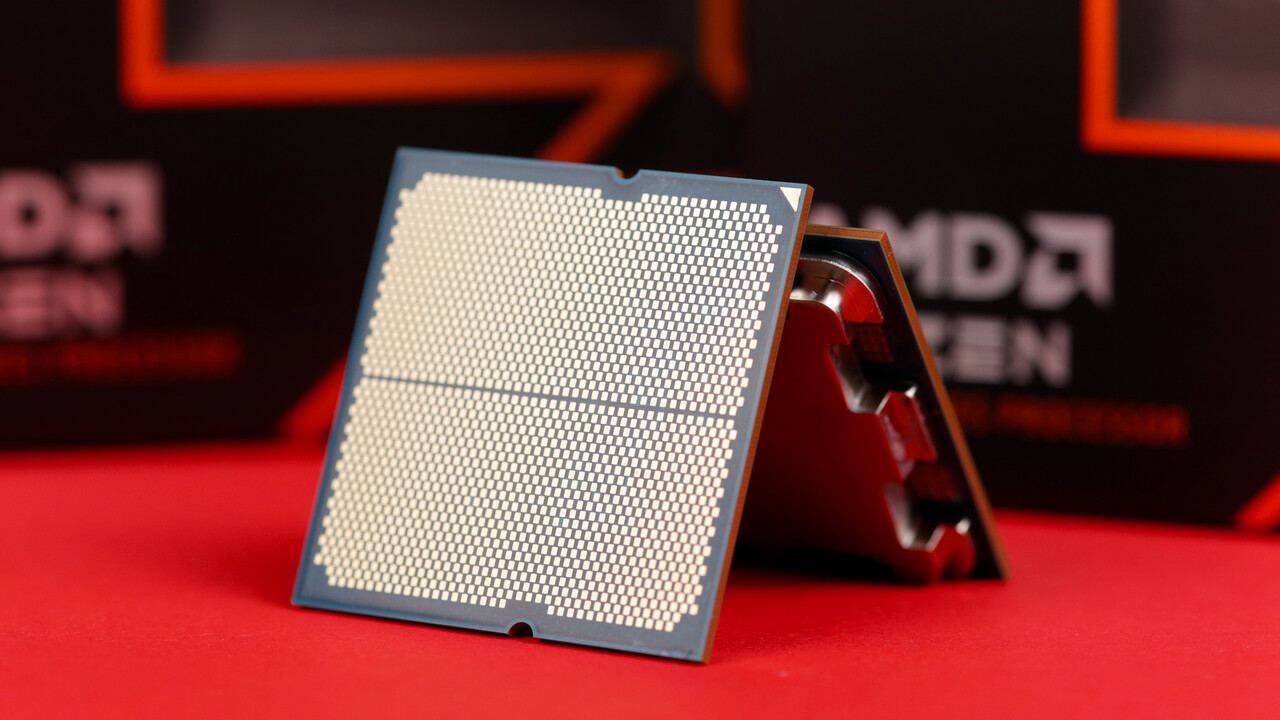

Image: AMD

AMD has successfully completed the next generation of EPYC processors for the HPC segment, codenamed Venice, in TSMC’s new N2 manufacturing process with nanosheets. Additionally, AMD successfully completed initial testing and validation of the 5th generation EPYC at TSMC Arizona Fab 21.

Industrial Product of the First HPC in TSMC N2

The next generation of EPYC processors, also known as Venice, is the world’s first industrial HPC product to successfully complete a process in TSMC’s N2 manufacturing process with nanosheets. AMD CEO Dr. Lisa Su and TSMC CEO Dr. CC Wei celebrated this demonstration with a wafer manufactured accordingly with Venice CCD. It’s in the new production

TSMC announced the N2 manufacturing process in the summer of 2022, with production expected to start in 2025. By moving to gate all around (GAA), or as TSMC calls it, nanosheets, they achieve 10 to 15% more power with the same power consumption, or 25 to 30% more power consumption with the same performance. A high-performance variant, now used in the HPC segment for AMD, as well as a mobile version, are planned for TSMC N2.

Nanosheets briefly explained

Nanosheets or nanowires are two-dimensional structures with a thickness of less than 100 nm. They have been on the chip industry’s roadmap for years and aim to make possible the successor technology to FINFET, which uses transistors in a three-dimensional fin structure. Nanosheets are being used for the first time with a surrounding gate, as this type of production relies on thin “wires.”

More details on the manufacturing technology: Innovations yesterday, today, and tomorrow

AMD Venice expected to launch next year

According to AMD’s latest announcement, the next generation of EPYCs is expected to hit the market next year. Venice, aka EPYC 9006, is expected to once again offer a maximum of 8 chip slots with up to 32 Zen-6 cores, thus up to 256 cores from 2nm production.

As “Turin Classic,” the current EPYC 9005 currently offers a maximum of 128 Zen-5 cores with 16 core CCDs and a maximum of 192 Zen-5c cores with 12 core CCDs as “Turin Dense.” Venice would again reduce the number of CCDs by four times. Officially, AMD has not yet announced any technical details about Venice. Successful Testing at TSMC Arizona Fab 21

Although N2 production is carried out in Taiwan, the current 5th generation EPYC processors are also to be manufactured in the United States at TSMC Arizona Fab 21. There, AMD successfully completed the “shrinkage” process, i.e., the initial testing after the production of a new chip and the validation of the processors.

Topics: AMD EPYC Half-Conductor Industry Processor Server TSMC Source: AMD

Marc deciphers processors by testing their performance for gaming, content creation, and artificial intelligence.