Fast Interface: The Final Draft for PCIe 7.0 is 49 comments

Image: pci-sig

With version 0.9, the PCI-SIG adopted the final draft for the specifications of the PCIE 7.0 interface standards. Manufacturers can now “internally verify the technology for their essential patents,” according to a press release. Functional changes are no longer expected.

If all goes according to plan, the full PCIe 7.0 specification should be published “this year.” Moreover, the deadline is not yet limited, as it was roughly dated 2025 long ago. But until the first-end PCIe 7.0 products are in use, a few more years will pass. The first conformance tests are planned for 2028 at the earliest. There is a slight delay here. This brings PCIe 7.0 to the table.

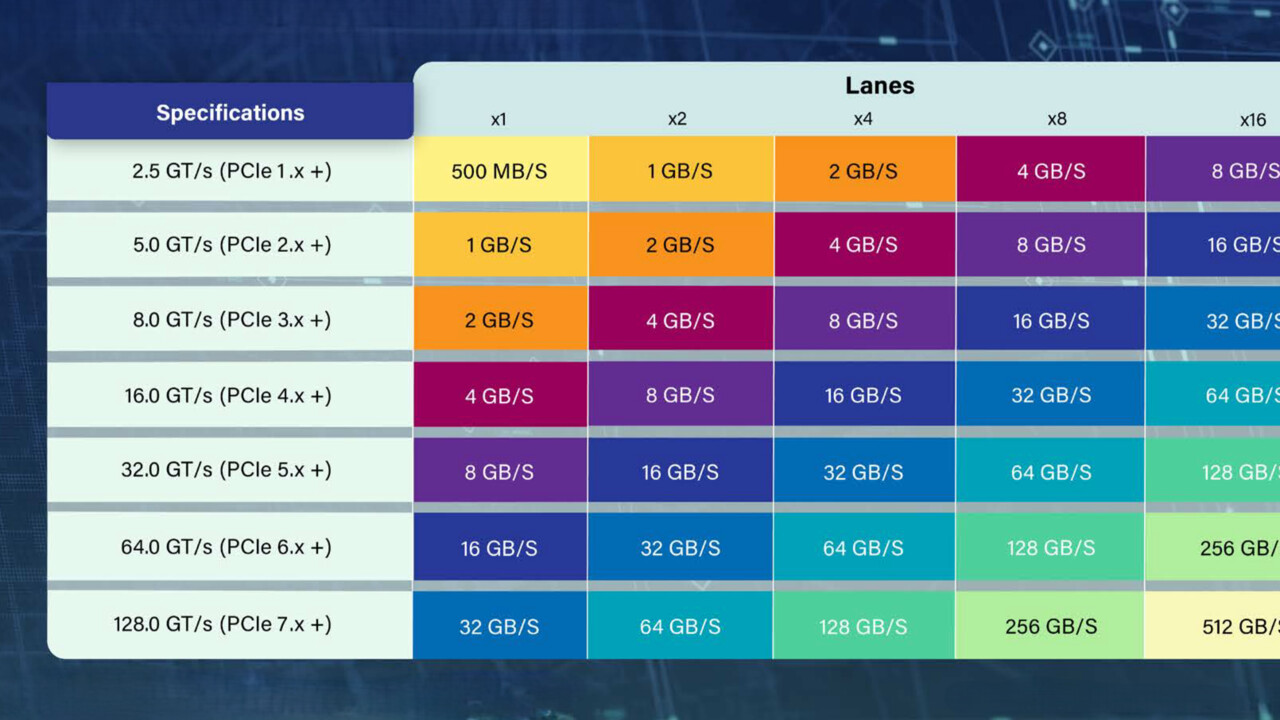

The transmission rate for PCIe 7.0 rises to approximately 16 GB/s per lane and direction. With a maximum configuration of 16 lanes (PCIe 7.0 x16), the speed is accordingly 256 GB/s. This is twice as fast as the current PCIe 6.0 standard.

However, since PCI Express allows dual simplex operation with simultaneous data transmission in both directions, the PCI-SIG announces 512 GB/s for PCIE 6.0, which is analogous to 256 GB/s. As with PCIe 6.0, four-stage pulse width modulation (PAM4) is used. Designed Application Areas

According to PCI-SIG, “data-intensive market segments” are addressed with PCIe 7.0 medium-sized areas such as high-performance computing (supercomputing), hyperscale data centers, cloud computing, and AI applications. PCIe 7.0 is also a concern for military and aviation networks or 800g.

The following points were formulated as the objectives of the new standard:

Delivering 128 GT/s raw bit rate and up to 512 GB/s bi-directionally via x16 configurationUtilizing PAM4 (Pulse Amplitude Modulation with 4 levels) signalingFocusing on the channel parameters and reachImproving power efficiencyContinuing to deliver the low-latency and high-reliability targetsMaintaining backwards compatibility with all previous generations of PCIe technology PCI-SIG

Today, there is no mention of work on an optical standard, which previous plans say should find its way into the PCIE 7.0 specification. In August 2023, the PCI-SIG Optical Working Group was launched to design matching form factors for the connections and transceiver. More throughput, lower latencies and a lower energy requirement are promised compared to transferring over copper lines.

Topics: PCI Express PCIe 7.0 Mainboards Source: PCI-SIG

Thomas analyses motherboards to reveal their secrets: performance, connectivity, and overclocking options.