EPYC-prosessorit: AMD viimeisteli Venetsian Venetsian onnistuneesti TSMC N2:ssa 34 kommentin perusteella

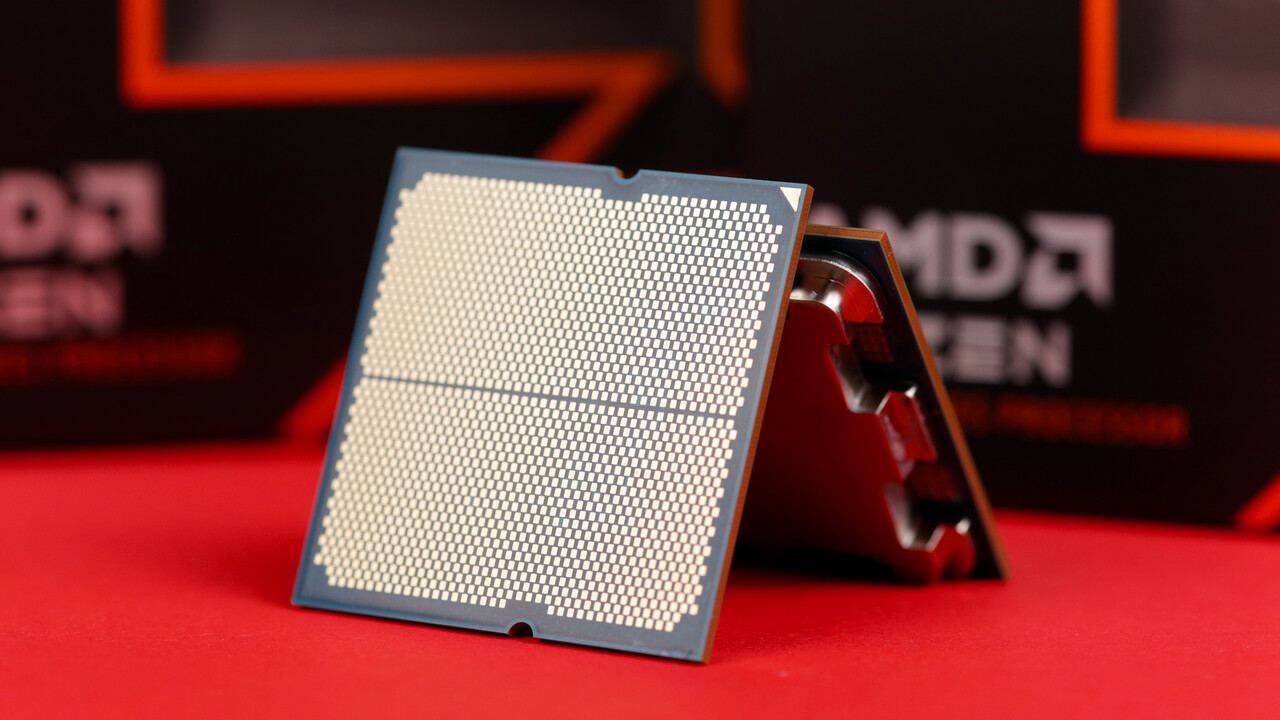

Kuva: AMD

AMD on onnistuneesti valmistanut seuraavan sukupolven EPYC-prosessoreja HPC-segmentille, koodinimeltään Venice, TSMC:n uudessa N2-nanolevyn valmistusprosessissa. Lisäksi AMD on suorittanut menestyksekkäästi 5. sukupolven EPYC:n varhaisen testauksen ja validoinnin TSMC Arizona Fab 21:ssä.

Ensimmäisen HPC:n teollisuustuote TSMC N2:ssa

Seuraavan sukupolven EPYC-prosessorit alias Venice on teollisuusmaailman ensimmäinen HPC-tuote, joka on onnistunut viimeistelemään nauhan TSMC N2 -valmistusprosessissa nanolevyillä. AMD:n toimitusjohtaja Dr. Lisa Su ja TSMC:n toimitusjohtaja tohtori CC Wei juhlivat tätä esittelyä kiekolla, joka on valmistettu Venetsian CCD:n mukaisesti.

Se on uudessa tuotannossa

TSMC oli julkistanut N2-valmistusprosessin kesällä 2022, jolloin tuotannon odotetaan alkavan vuonna 2025 ja siirtymällä gate all around (GAA) tai kuten TSMC sitä kutsuu: nanolevyt, 10-15% enemmän samalla virrankulutuksella tai 25-30% enemmän virrankulutusta samalla suorituskyvyllä. TSMC N2:lle suunnitellaan korkean suorituskyvyn muunnelmaa, jota käytetään nyt AMD:n HPC-segmentissä, sekä mobiiliversiota.

Nanosheets selitetty lyhyesti

Nanolevyt tai nanolangat ovat kaksiulotteisia rakenteita, joiden paksuus on alle 100 nm. Ne ovat olleet siruteollisuuden tiekartalla vuosia ja pyrkivät mahdollistamaan FINFETin seuraajateknologian, joka käyttää transistoreita kolmiulotteisessa riparakenteessa. Nanosarkkeja käytetään ensimmäistä kertaa ympäröivän portin kanssa, koska tämäntyyppinen tuotanto perustuu ohuisiin ”johtoihin”.

Lisätietoja valmistustekniikasta: Innovaatioita eilen, tänään ja huomenna

AMD Venice käynnistyy ensi vuonna

AMD:n tämänhetkisen ilmoituksen mukaan seuraavan sukupolven EPYC:n odotetaan saapuvan markkinoille ensi vuonna. Venice Alias EPYC 9006 tarjoaa jälleen enintään 8 sirupaikkaa, joissa on jopa 32 Zen-6-ytimistä ja siten jopa 256 ydintä 2 nm:n tuotannosta.

”Turin Classicina” nykyinen EPYC 9005 -alias tarjoaa tällä hetkellä enintään 128 ZEN-5-ydintä 16 88-ytimisellä CCD:llä ja enintään 192 zen-5c-ydintä 12 16-kernisellä CCD:llä nimellä ”Turin Dense”. Venetsia vähentäisi CCDS:ien määrää jälleen neljä kertaa. Virallisella puolella AMD ei ole vielä ilmoittanut mitään teknisiä yksityiskohtia Venetsiasta.

Onnistunut testaus TSMC Arizona Fab 21:ssä

Vaikka N2:n tuotanto tapahtuu Taiwanissa, nykyiset 5. sukupolven EPYC-prosessorit on tarkoitus valmistaa myös Yhdysvalloissa TSMC Arizona Fab 21:ssä. Siellä AMD on onnistuneesti saattanut päätökseen ”kutistumisen”, eli ensimmäisen testauksen uuden sirun valmistuksen ja prosessorien validoinnin jälkeen.

Aiheet: AMD EPYC Half-Conductor Industry Processor Server TSMC Lähde: AMD

Marc analysoi prosessoreita testaamalla niiden suorituskykyä pelaamiseen, sisällöntuotantoon ja tekoälyyn.