Voci credibili: AMD Ryzen 9 9950X3D e 9900X3D fine gennaio con 1 × cache 164 commenti

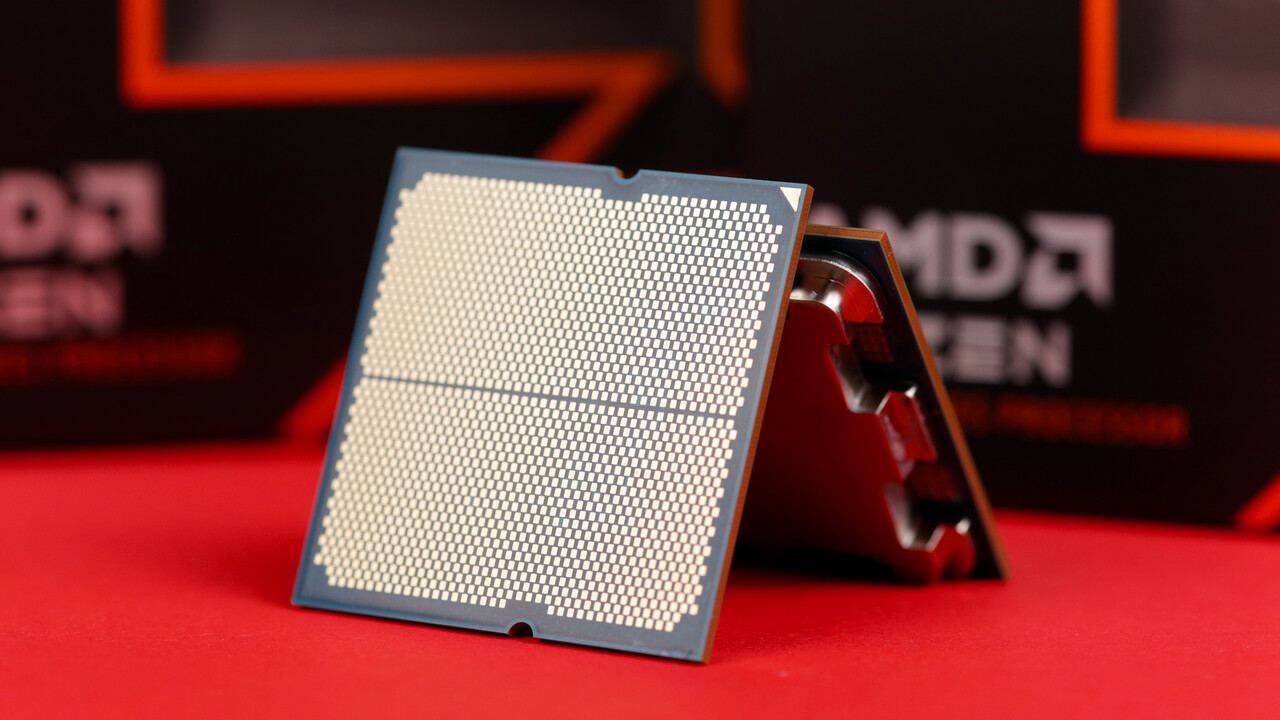

Quando AMD Ryzen 9 9950X3D e Ryzen 9 9900X3D con due chipset rispettivamente per 16 e 12 core CPU seguiranno il Ryzen 7 9800X3D (test) e offriranno per la prima volta V-Cache 3D aggiuntiva su ciascun chiplet? L’account X Hoang Anh Phu, che è stato più volte preciso riguardo ad AMD, vorrebbe avere una risposta a queste due domande.

Fine gennaio con un chiplet 3D V-Cache

Quindi, il Ryzen 9 9950X3D con 16 core e il Ryzen 9 9900X3D con 12 core Zen 5 appariranno alla fine di gennaio e dovrebbero essere presentati da AMD al CES 2025 all’inizio di gennaio. Entrambi i chiplet non devono essere dotati di 3D V-Cache.

AMD probabilmente ha deciso di non farlo perché pochissimi giochi beneficiano di più di otto core. In genere, è sufficiente eseguire solo thread di gioco sul chipset X3D per le varianti a 12 e 16 core utilizzando il driver del chipset e l’aiuto della Xbox Game Bar.

Due chiplet con cache non hanno solo vantaggi

Di solito funziona, ma non sempre: Stalker 2 (test), ad esempio, non è stato riconosciuto come gioco quando è stato lanciato la scorsa settimana e funzionava sul chiplet sbagliato nella barra di gioco senza intervento manuale. Questo era ancora il caso di Outcast – A New Beginning (recensione) anche mesi dopo l’uscita. In questo caso, gli utenti devono completare l’assegnazione manualmente utilizzando l’overlay di Xbox Game Bar.

Due chipset X3D eviterebbero questo percorso soggetto a errori, ma renderebbero anche il processore più costoso. Tuttavia, consentire generalmente ai giochi di funzionare su tutti i 16 core raramente avrebbe alcun vantaggio reale e talvolta avrebbe anche uno svantaggio, quando i giochi con più di 8 core e 16 thread causano problemi.

Argomenti: Processori AMD AMD Granite Ridge AMD Ryzen 9000 Ryzen Zen Fonte: X (Twitter)

Marc decodifica i processori testando le loro prestazioni per gaming, creazione di contenuti e intelligenza artificiale.