EPYC-processorer: AMD slutför framgångsrikt Venedig i Venedig i TSMC N2 från 34 kommentarer

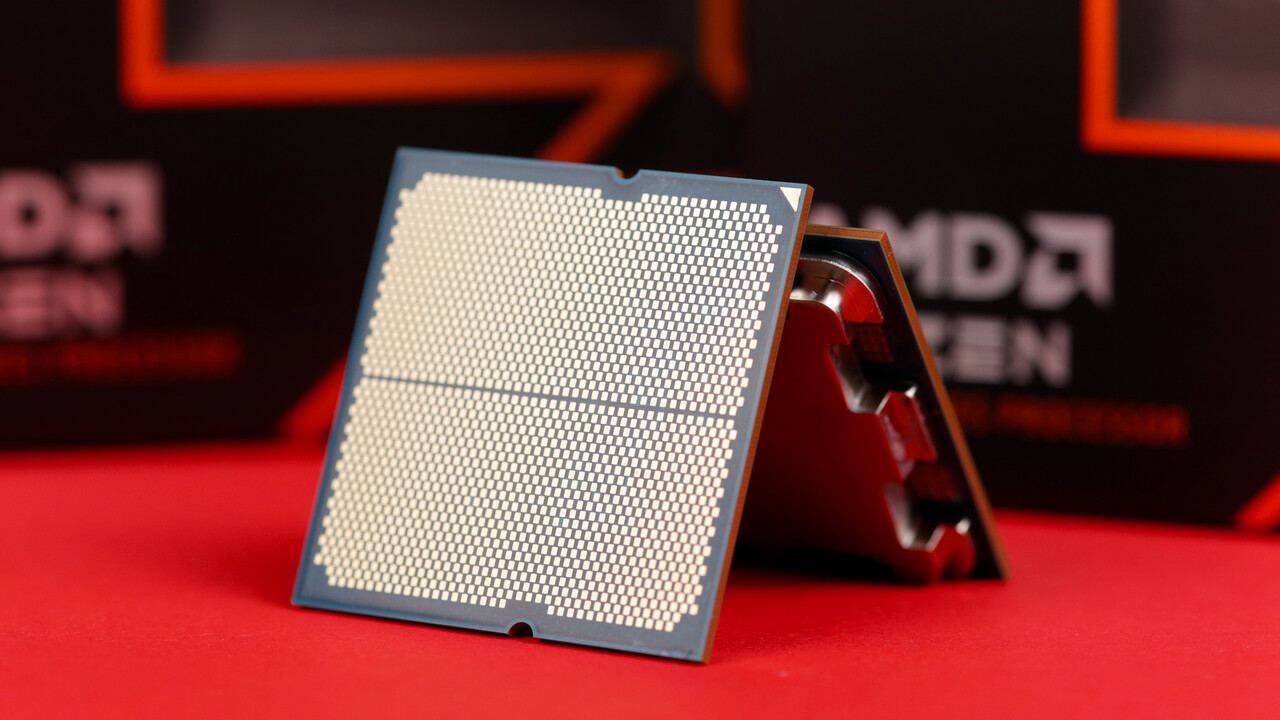

Bild: AMD

AMD har framgångsrikt tillverkat nästa generation av EPYC-processorer för HPC-segmentet, kodnamnet Venedig, i TSMC:s nya N2 nanosheet tillverkningsprocess. Dessutom har AMD framgångsrikt genomfört tidig testning och validering av 5:e generationens EPYC vid TSMC Arizona Fab 21.

Industriell produkt från den första HPC:n i TSMC N2

Nästa generation av EPYC-processorer aka Venedig är den industriella världens första HPC-produkt som framgångsrikt slutför en remsa i TSMC N2-tillverkningsprocessen med nanoark. AMD:s VD Dr. Lisa Su och TSMC:s VD Dr. CC Wei firade denna demonstration med en wafer tillverkad i enlighet med Venedig CCD.

Det är i den nya produktionen

TSMC hade annonserat N2-tillverkningsprocessen sommaren 2022 med en förväntad produktionsstart 2025 och, genom att flytta till gate all around (GAA), eller som TSMC kallar det: nanoark, 10-15% mer med samma strömförbrukning eller 25-30% mer strömförbrukning med samma prestanda. En högpresterande variant som nu används i HPC-segmentet för AMD, samt en mobilversion planeras för TSMC N2.

Nanosheets förklaras kort

Nanosheets eller nanotrådar är tvådimensionella strukturer med en tjocklek mindre än 100 nm. De har funnits på chipindustrins färdplan i flera år och syftar till att göra FINFET:s efterföljande teknologi, som använder transistorer i en tredimensionell fenstruktur, möjlig. Nanosheets används för första gången med en omgivande grind, eftersom denna typ av produktion är beroende av tunna ”trådar”.

Mer information om tillverkningstekniken: Innovationer igår, idag och imorgon

AMD Venedig väntas starta nästa år

Enligt AMD:s aktuella tillkännagivande förväntas nästa generation av EPYC komma ut på marknaden nästa år. Venedig AliasEPYC 9006 bör återigen erbjuda maximalt 8 chip-slots med upp till 32 Zen-6-kärnor och därmed upp till 256 kärnor från 2nm-produktion.

Som ”Turin Classic” erbjuder det nuvarande EPYC 9005-aliaset för närvarande maximalt 128 ZEN-5-kärnor med 16 8 8-kärnor CCD och maximalt 192 zen-5c-kärnor med 12 16-kärn CCD:er som ”Turin Dense”. Venedig skulle återigen minska antalet CCDS med fyra gånger. På den officiella sidan har AMD ännu inte meddelat några tekniska detaljer om Venedig.

Framgångsrik testning på TSMC Arizona Fab 21

Även om N2-tillverkning utförs i Taiwan så ska den nuvarande 5:e generationens EPYC-processorer även tillverkas i USA på TSMC Arizona Fab 21. Där har AMD framgångsrikt genomfört ”krympningen”, det vill säga den initiala testningen efter tillverkningen av ett nytt chip och valideringen av processorerna.

Ämnen: AMD EPYC Half-Conductor Industry Processor Server TSMC Källa: AMD

Marc analyserar processorer genom att testa deras prestanda för spel, innehållsskapande och artificiell intelligens.